The Digital Electronics GATE questions from the previous years along with the sample questions must be thoroughly practised to perform well in the exam. The question papers are a good source where the candidates can learn about the pattern and model of questions.

Table of Contents

The Digital Electronics GATE questions of all types must be practised by the aspirants wishing to crack the GATE exam with good numbers. Practising the question papers regularly helps the candidates develop exam hall strategies as well as time management skills that help them during the exam.

The GATE 2024 is scheduled to be conducted on Feb 3, Feb 4, Feb 10 and Feb 11, 2024. Candidates can check their responses on the GATE 2024 response sheet which will be released on the official website on Feb 16, 2024.

The Digital Electronics questions will come from the important topics within the GATE CSE syllabus. Solving the questions is an efficient way of preparing for the GATE exam.

Digital Electronics GATE Questions with Answers - Download PDF

The PDF containing the important questions from previous years along with the answers have been attached in the table below. Candidates can refer to the PDF for practice.

| Digital Electronics GATE Questions with Answers | Download PDF |

Practice Now: GATE Previous Year Question Paper

Top 15+ Digital Electronics GATE Questions with Answers

The aspirants of the GATE 2024 must practise the questions papers regularly, to crack the examination. Digital Electronics is a significant section under the GATE CSE syllabus. Candidates must practise the GATE question papers and model questions to strengthen their preparation for the exam. The GATE answer keys and question papers from the previous years GATE exams are a great source of practice for the aspirants.

Shared below is a list of the top 15+ Digital Electronics GATE questions along with the answers.

- In 16-bit 2’s complement representation, the decimal number -28 is:

(A) 0000 0000 1110 0100

(B) 1000 0000 1110 0100

(C) 1111 1111 0001 1100

(D) 1111 1111 1110 0100

Ans: (D) 1111 1111 1110 0100

- The minters expansion of f(P, Q, R) = PQ + QR’ + P’R’ is

(A) m2 + m4 + m6 + m7

(B) m0 + m1 + m3 + m5

(C) m0 + m1 + m6 + m7

(D) m2 + m3 + m4 + m5

Ans: (A) m2 + m4 + m6 + m7

Also Check: GATE CSE Question Papers 2024: Answer Keys, Previous Years PDF

- Which one of the following is NOT a valid identity?

(A) (x ⊕ y) ⊕ z = x ⊕ (y ⊕ z)

(B) (x + y) ⊕ z = x ⊕ (y + z)

(C) x ⊕ y = x + y, if xy = 0

(D) x ⊕ y = (xy + x′y′)′

Ans: (B) (x + y) ⊕ z = x ⊕ (y + z)

- Which one of the following expressions does NOT represent the exclusive NOR of x and y?

(A) xy + x’y’

(B) x⊕y’

(C) x’⊕y

(D) x’⊕y’

Ans: (D) x’⊕y’

Also Read: GATE CSE Paper Analysis 2024: Difficulty Level, Weightage

- Consider a 4-bit Johnson counter with an initial value of 0000. The counting sequence of this counter is

(A) 0, 1, 3, 7, 15, 14, 12, 8, 0

(B) 0, 1, 3, 5, 7, 9, 11, 13, 15, 0

(C) 0, 2, 4, 6, 8, 10, 12, 14, 0

(D) 0, 8, 12, 14, 15, 7, 3, 1, 0

Ans: (D) 0, 8, 12, 14, 15, 7, 3, 1, 0

- The minimum number of 2-input NAND gates required to implement a 2-input XOR gate is

(A) 4

(B) 5

(C) 6

(D) 7

Ans: (A) 4

Also Read: Last Minute Preparation Tips for GATE 2024

- A 16 Kb (=16,384 bit) memory array is designed as a square with an aspect ratio of one (number of rows is equal to the number of columns). The minimum number of address lines needed for the row decoder is ____________

(A) 10

(B) 7

(C) 5

(D) 1

Ans: (B) 7

- A traffic signal cycles from GREEN to YELLOW, YELLOW to RED and RED to GREEN. In each cycle, GREEN is turned on for 70 seconds, YELLOW is turned on for 5 seconds and the RED is turned on for 75 seconds. This traffic light has to be implemented using a finite state machine (FSM). The only input to this FSM is a clock of 5 second period. The minimum number of flip-flops required to implement this FSM is _______

(A) 5

(B) 7

(C) 10

(D) 15

Ans: (a)

Also Read: GATE Qualifying Marks 2024: Passing Marks, Admission Cutoff

- Consider a four bit D to A converter. The analog values corresponding to digital signals of values 0000 and 0001 are 0 V and 0.0625 V, respectively. The analog value (in Volts ) corresponding to the digitals signal 1111 is ______________

(A) 0.93

(B) 0.95

(C) 0

(D) 1

Ans: (A) 0.93

- A traffic signal cycles from GREEN to YELLOW, YELLOW to RED and RED to GREEN. In each cycle, GREEN is turned on for 70 seconds, YELLOW is turned on for 5 seconds and the RED is turned on for 75 seconds. This traffic light has to be implemented using a finite state machine (FSM). The only input to this FSM is a clock of 5 second period. The minimum number of flip-flops required to implement this FSM is _______

(A) 5

(B) 7

(C) 10

(D) 15

Ans: (A) 5

Also Read: GATE Books for CSE 2024: Exam Pattern, Preparation Tips

- The number of comparators in 4-bit flash ADC is

(A) 4

(B) 5

(C) 15

(D) 16

Ans: (C) 15

- The number of comparators required in a 3-bit comparator type ADC is

(A) 2

(B) 3

(C) 7

(D) 8

Ans: (C) 7

Also Read: GATE Subject Wise Weightage 2024: Chapter-wise Topic

- In a DRAM,

(A) Periodic refreshing is not required

(B) Information is stored in a capacitor

(C) Information is stored in a latch

(D) Both read and write operations can be performed simultaneously

Ans: (B) Information is stored in a capacitor

- A 16 Kb (=16,384 bit) memory array is designed as a square with an aspect ratio of one (number of rows is equal to the number of columns). The minimum number of address lines needed for the row decoder is ____________

(A) 10

(B) 7

(C) 5

(D) 1

Ans: (B) 7

Also, Check: DBMS GATE Questions with Answers - Download PDF

- A bulb in a staircase has two switches, one switch being on the ground floor and the other one on the first floor. The bulb can be turned ON and also can be turned OFF by any one of the switches, irrespective of the state of the other switch. The logic of switching of the bulb resembles.

(A) An AND gate

(B) An OR gate

(C) An XOR gate

(D) A NAND gate

Ans: (C) An XOR gate

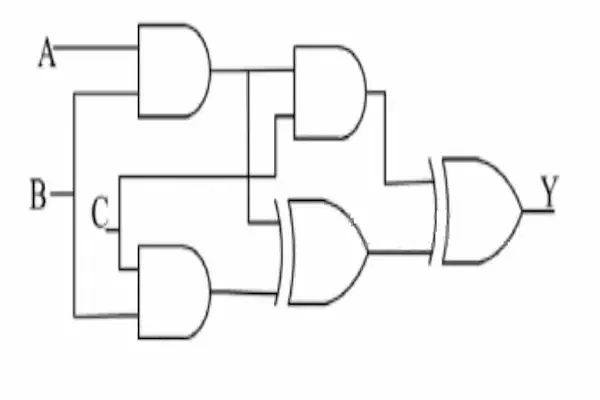

- The output of the combinational circuit given below is

(A) A+B+C

(B) A(B+C)

(C) B(+A)

(D) C(A+B)

Ans: (C) B(+A)

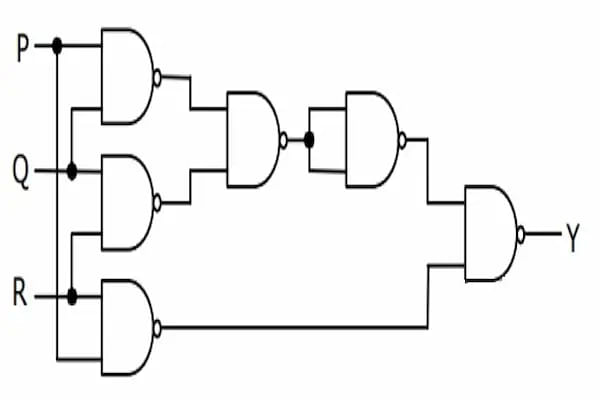

- The output Y in the circuit below is always ‘1’ when

(A) Two or more of the inputs P, Q, R are ‘0’

(B) Two or more of the inputs P, Q, R are ‘1’

(C) Any odd number of the inputs P, Q, R is ‘0’

(D) Any odd number of the inputs P, Q, R is ‘1’

Ans: (B) Two or more of the inputs P, Q, R are ‘1’

Also Read: Importance of GATE Mock Tests 2024 for Effective Preparation

![Indian Institute of Technology, [IIT] Bombay](https://media.getmyuni.com/azure/college-image/small/indian-institute-of-technology-iit-bombay.jpg)

![Indian Institute of Technology, [IIT] Kanpur](https://media.getmyuni.com/azure/college-image/small/indian-institute-of-technology-iit-kanpur.jpg)

![Indian Institute of Technology, [IIT] Kharagpur](https://media.getmyuni.com/azure/college-image/small/indian-institute-of-technology-iit-kharagpur.jpg)

POST YOUR COMMENT